台积电首次公布2nm制程工艺,2025年量产

导读:6月17日消息,钛媒体App获悉,今天凌晨举行的台积电北美技术论坛上,台积电(TSMC)正式公布未来先进制程路线图。

2021年世界半导体大会的台积电展台(图片来源:钛媒体App编辑)

传闻许久的2nm终于来了。

6月17日消息,钛媒体App获悉,今天凌晨举行的台积电北美技术论坛上,台积电(TSMC)正式公布未来先进制程路线图。

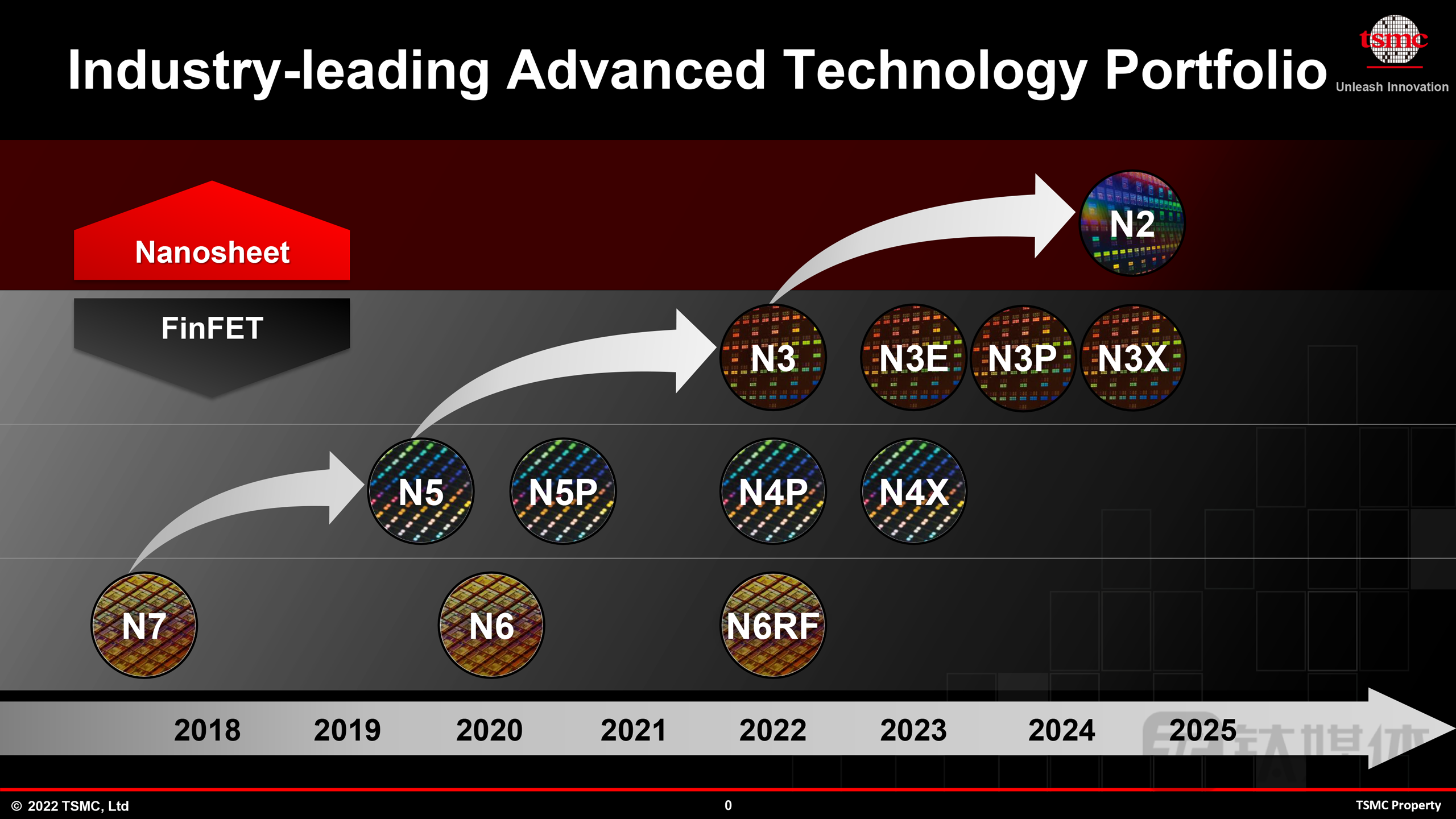

其中,台积电3nm(N3)工艺将于2022年内量产,而台积电首度推出采用纳米片晶体管(GAAFET)架构的2nm(N2)制程工艺,将于2025年量产。

台积电总裁魏哲家在线上论坛表示,身处快速变动、高速成长的数字世界,对于运算能力与能源效率的需求较以往更快速增加,为半导体产业开启前所未有的机会与挑战。值此令人兴奋的转型与成长之际,台积电在技术论坛揭示的创新成果彰显了台积电的技术领先地位,以及支持客户的承诺。

与此同时,台积电研发资深副总裁米玉杰(YJ Mii)在这场会议上宣布,台积电会在2024年拥有光刻机巨头ASML最新的high-NA极紫外光(EUV)光刻机微影设备。“主要用于合作伙伴的研究目的......针对客户需求,开发相关基础架构与格式的解决方案,推动创新。”

台积电制造工艺路线图,2nm于2025年开始量产

具体来说,此次台积电技术峰会上,核心是公布N3(3nm级)和N2(2nm级)系列的领先节点具体技术细节,以及TSMC-3DFabricTM 三维矽晶堆叠解决方案,从而在未来几年用于制造先进的CPU、GPU和移动SoC芯片产品中。

3nm技术节点:台积电第一个3nm级节点称为N3,有望在今年下半年开始大批量制造 (HVM)量产,预计2023年初交付给客户。其中,3nm第二节点N3E,与N5相比,在相同的速度和复杂性下,N3E功耗降低34%,性能提升18%,逻辑晶体管密度提高1.6倍,而且搭配先进的TSMC FinFlextm架构,能够精准协助客户完成符合其需求的系统单芯片设计。

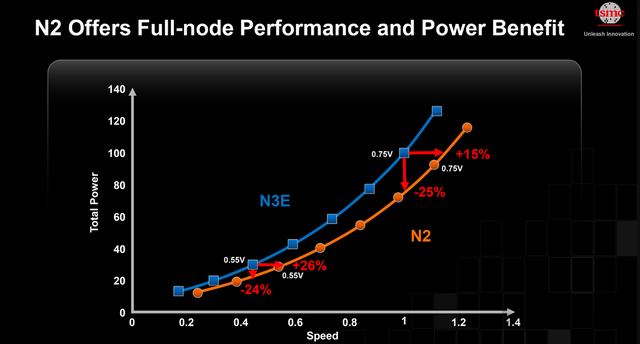

2nm技术节点:台积电第一个2nm级节点称为N2,采用纳米片晶体管(GAAFET)架构,预计于2025年开始量产。据悉,在相同功耗下,2nm性能速度较3nm增快10%至15%,若在相同速度下,功耗降低25%至30%。台积电还表示,2nm制程技术平台也涵盖高效能版本及完备的小晶片(Chiplet)整合解决方案。

扩大超低功耗平台:台积电称正在开发N6e技术,专注于边缘人工智能及物联网设备。N6e将以7nm制程为基础,逻辑密度可望较上一代的N12e多3倍。据悉,N6e平台涵盖逻辑、射频、类比、嵌入式非挥发性存储器、以及电源管理IC解决方案。

TSMC-3DFabricTM 三维矽晶堆叠方案:台积电今天展示两项突破性创新,一项是以SoIC为基础的CPU,采用晶片堆叠于晶圆之上(Chip-on-Wafer,CoW)技术来堆叠三级快取静态随机存取存储;另一项是创新的AI SoC,采用晶圆堆叠于晶圆之上(Wafer-on-Wafer,WoW)技术堆叠于深沟槽电容晶片之上。

台积电表示,搭载CoW及WoW技术的7nm芯片,目前已经量产,5nm技术预计于2023年完成。为满足客户对于系统整合芯片及其他3DFabric系统整合服务需求,首座全自动化3D Fabric晶圆厂预计于2022年下半年开始生产。

随着台积电2nm转向基于纳米片的GAAFET架构,3nm系列将成为台积电FinFET节点最后一个技术平台。预计在2025年量产2nm芯片后,台积电仍将继续生产3nm半导体产品。

此外,台积电透露,到2025年,其成熟和专业节点的产能将扩大约 50%。该计划包括在台南、高雄、日本和南京建设大量新晶圆厂,此举将进一步加剧台积电与格芯、联电、中芯国际等晶圆代工厂商之间的竞争。

根据AnandTech报道,扩张成熟和专业节点投资的四个新设施分别为:台积电日本熊本的Fab 23一期厂,制造12nm、16nm、22nm和28nm芯片,并将拥有每月高达4.5万片300毫米(12寸)晶圆的生产能力;台南Fab 14第8期;高雄Fab 22二期;南京的Fab 16 1B 期,目前主要生产28nm成熟工艺芯片。

目前,台积电在全球共有13座晶圆代工厂。其中,10家工厂位于中国台湾地区,2家分别在上海和南京,分别制造8寸和12寸晶圆;1家在美国Fab11,制造8寸晶圆。而台积电7nm、5nm先进工艺芯片主要在台南Fab18厂进行生产。

作者|林志佳