AI算力产业链梳理:AIGC场景增多驱动算力需求提升

导读:ChatGPT 是目前为止最先进的语言生成模型之一,使用基于 GPT3 5 架构的大型语言模型(LLM),并通过强化学习进行训练,拥有语言理解和文本生成能力, 适用于问答、对话、生成文本等多种场景。

(报告出品方/作者:安信证券,马良、程宇婷)

1.ChatGPT浪潮带动算力需求提升,以GPU为核心的硬件市场扩容

1.1.ChatGPT:基于生成式AI技术的大型语言模型,商业化迅速开启

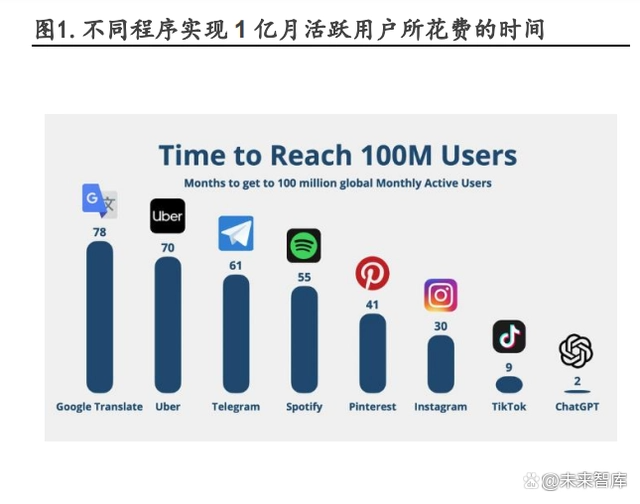

ChatGPT(ChatGenerativePre-trainedTransformer)是由OpenAI开发的聊天机器人程序,于2022年11月推出。ChatGPT是目前为止最先进的语言生成模型之一,使用基于GPT3.5架构的大型语言模型(LLM),并通过强化学习进行训练,拥有语言理解和文本生成能力,适用于问答、对话、生成文本等多种场景。ChatGPT用户规模扩增迅速,根据SimilarWeb数据,2023年1月期间,ChatGPT平均每天大约有1300万独立访客,数量是2022年12月的两倍多(Similarweb数据);根据瑞银公开报告数据,2023年1月(即上线两个月后)实现全球1亿月活跃用户,是历史上增长最快的消费者应用程序。ChatGPT是生成式AI在文字生成领域的应用,创造能力是其核心优势。传统AI依靠逻辑进行分类和判断,而生成式AI的壁垒在于能够创造新内容,可以是多模态的、模仿人类情感的、具有互动和审美性质的。传统的聊天机器人(Chatbot),例如客服机器人,只能根据用户输入的内容在数据库中查询到对应答案,再机械地以模板的形式反馈给客户;而ChatGPT采取生成式AI技术,并且有工作人员每日优化模型,在应对用户提问时会根据上下文内容调整回答内容,增强互动式、对话式的情感体验,更加智能。

OpenAI开放API,降本90%扩大覆盖用户面。2023年3月1日,OpenAI官网宣布ChatGPT和Whisper(OpenAI去年发行的语音识别生成模型)的API开放使用,开发者可将模型集成到APP和其他产品中。ChatGPTAPI接入的模型为GPT-3.5-turbo,与GPT-3.5相比更加快捷、准确,成本也更低,定价为每1000个tokens(约750个单词)0.002美元,用户则需要按照输入和输出的tokens总数来付费。OpenAI官方表示自2022年12月以来ChatGPT降低了90%的成本,开放API旨在使更多人受益于生成式AI技术。

1.2.采用GPT-3.5预训练模型,参数量随模型换代呈指数型增长

GPT3.5是一种大型语言模型(LLM),参数量大,精准度高。GPT-3.5采用深度学习中的Transformer架构,并通过大规模预训练(pre-training)的方式来学习自然语言处理任务,可以进行文本生成、对话生成、文本分类、命名实体识别、关键词提取等自然语言处理任务。

语言模型(LM)是指对语句概率分布的建模。具体是判断语句的语序是否正常,是否可以被人类理解。它根据句子中先前出现的单词,利用正确的语序预测句子中下一个单词,以达到正确的语义。例如,模型比较“我是人类”和“是人类我”出现的概率,前者是正确语序,后者是错误语序,因此前者出现的概率比后者高,则生成的语句为“我是人类”。

大型语言模型(LLM)是基于海量数据集进行内容识别、总结、翻译、预测或生成文本等的语言模型。相比于一般的语言模型,LLM识别和生成的精准度会随参数量的提升大幅提高。

ChatGPT需要通过预训练来形成GPT3.5的模型,从而可以在用户端的网页或APP进行推理。预训练指先通过一部分数据进行初步训练,再在这个初步训练好的模型基础上进行重复训练,或者说是“微调”;推理指将预训练学习到的内容作为参考,对新的内容进行生成或判断。预训练是模型运作的主要部分,所需要的精度较高,算力需求也较高;推理则相反。

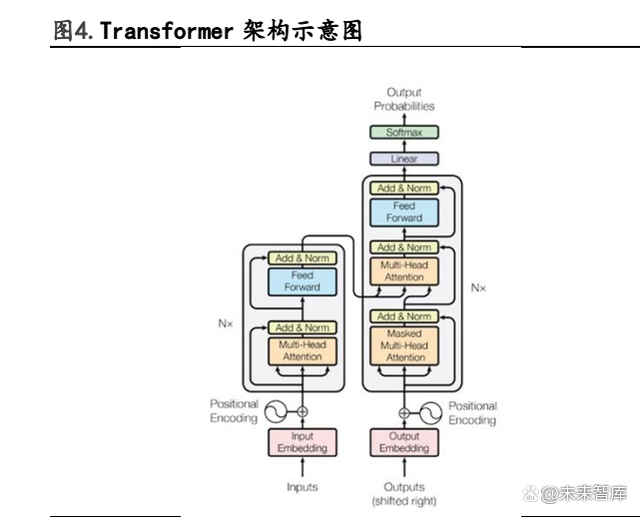

ChatGPT通过Transformer和RLHF两种语言模型进行预训练,可并行训练并大量优化反馈。采用深度学习中的Transformer架构,并通过大规模预训练(pre-training)的方式来学习自然语言处理任务,可以进行文本生成、对话生成、文本分类、命名实体识别、关键词提取等自然语言处理任务。

长短期记忆网络算法(LSTM)是一种时间循环神经网络。传统的循环神经网络(RNN)拥有链式形式,就像人脑会忘记很久以前发生的事件,RNN也会忘记它在较长序列中学习的内容,因此具有短时记忆。LSTM是一种特殊的RNN,它解决了传统RNN的短时记忆问题,在Transformer问世前曾主导NLP领域,但也拥有无法并行训练、建模长度有限的缺点。

Transformer是一个完全依赖于自注意力机制来计算其输入和输出的表示的转换模型,所以与LSTM的顺序处理不同,它可以并行同时处理所有的输入数据,模仿人类联系上下文的习惯,从而更好地为LLM注入意义并支持处理更大的数据集。

人类反馈信号强化学习(RLHF)指使用强化学习的方式直接优化带有人类反馈的语言模型,使得语言模型能够与复杂的人类价值观“对齐”。它负责ChatGPT预训练中微调的部分,首先在人类的帮助下训练一个奖赏网络(RM),RM对多个聊天回复的质量进行排序,从而增加ChatGPT对话信息量,使其回答具有人类偏好。

ChatGPT的预训练需要处理海量参数,从而实现超高文本识别率。OpenAI目前没有公布ChatGPT所使用的GPT-3.5的相关数据,由表2可知,随着新模型推出,新的参数量需求呈翻倍式增长。OpenAI首席执行官SamAltman接受公开采访表示,GTP-4参数量为GTP-3的20倍,需要的计算量为GTP-3的10倍;GTP-5在2024年底至2025年发布,它的参数量为GTP-3的100倍,需要的计算量为GTP-3的200-400倍。

GPT-4功能升级,多模态拓展应用场景。2023年3月14日,OpenAI正式发布GPT-4模型,早于此前23年下半年发布的时间规划。根据OpenAI官方,GPT-4模型于2022年8月完成训练,之后通过6个月时间对模型进行了安全性研究、风险评估和迭代。GPT-4作为大型多模态模型,在多方面提升显著:1)多模态大模型——新增接受图片和文本输入并产生文本输出能力,能分析图片的符号意义,如理解图片中的“笑梗”;文字方面,GPT-4的输入限制由3000字提升至2.5万字,对于英语以外的语种支持有更多优化。2)提升各种专业和学术水准并有较好表现。能处理更长更复杂的文本,在没有针对考试内容进行特别训练的基础上,GPT-4在各项测试中均取得较高成绩,如GPT-4在GRE考试中取得332+4分,GPT-4(novision)取得322+4分,而GPT-3.5分数为301+4分。3)在安全、一致性上有较为明显的提升。根据OpenAI的对抗性测试和红队测试结果,相比GPT-3.5,GPT-4产生客观事实回答的可能性提升40%,响应违禁内容请求的可能性降低82%。

根据公开新闻整理,目前接入GPT-4支持的应用端已有微软的必应浏览器newBing、嵌入于办公软件的Microsoft365Copilot人工智能服务,外语培训教育机构多邻国的付费产品DuolingoMax、摩根士丹利等。我们认为,随着GPT-4等模型复杂度升级,并逐步支持图片视频识别等多模态,对应的算力及基础设施需求有望持续增长;下游则有望拓展更多图片视频内容端的商业化应用场景。

1.3.海量参数产生大算力需求,GPGPU等高壁垒AI芯片受益

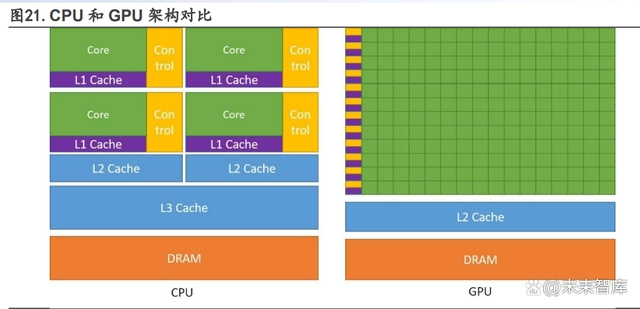

ChatGPT算力需求与参数量呈正相关,对硬件的内存容量和带宽提出高要求。算力即计算能力,具体指硬件对数据收集、传输、计算和存储的能力,算力的大小表明了对数字化信息处理能力的强弱,常用计量单位是FLOPS(Floating-pointoperationspersecond),表示每秒浮点的运算次数。硬件方面,运算量取决于GPU运算执行时间的长短,而参数量取决于占用显存的量。运算量(FLOPS)的数值通常与参数量(parametercount)成比例,不同模型架构的换算关系不同。模型越复杂、参数量越大,所需计算量越大。GPGPU拥有硬件技术的核心壁垒:大显存带宽,进行超高能效比的并行运算,可同时用于GPT模型的训练和推理过程。GPGPU(通用图像处理器)是一种由GPU去除图形处理和输出,仅保留科学计算、AI训练和推理功能的GPU(图形处理器)。GPU芯片最初用于计算机系统图像显示的运算,但因其相比于擅长横向计算的CPU更擅长于并行计算,在涉及到大量的矩阵或向量计算的AI计算中很有优势,GPGPU应运而生。目前,GPGPU的制造工艺在英伟达等企业的领导下已趋向成熟,成本在AI芯片中也较低,成为市场主流选择,ChatGPT引起的AI浪潮有望提升其应用规模。

FPGA具有可编程的灵活性,ASIC性能佳、具有定制化特点,但成本方面与GPU相比稍显劣势,在GPT等AI模型的运用占比较GPU低。FPGA指现场可编程逻辑门阵列,具有静态可重复编程和动态在系统重构的特性,但其开发难度大、只适合定点运算,同时价格也比较昂贵,性能方面也不及GPU与ASIC,只在精度较低的推理过程有所应用。ASIC指专用集成电路,是一种应不同用户需求和不同系统需要而设计、制造的集成电路。ASIC芯片的性能较GPU佳,能耗也较低,但因其定制性价格昂贵,在人工智能平台和推理过程中有部分应用。

1.4.类ChatGPT成本高昂产品涌现,国产大模型方兴未艾

大模型运行成本高昂,准入壁垒较高。大模型对于训练时间和参数量都有高要求,以OpenAICEOAltman在推特上回复马斯克的留言可知,ChatGPT平均一次聊天成本为几美分。根据SimilarWeb数据,2023年1月27日至2月3日ChatGPT日活跃用户达2500万人。中性假设下,以平均单人单日对话7次,每次3美分成本进行测算,对应一年支出对话成本约为19.2亿美元。根据英伟达官网,A100作为DGXA100系统的一部分进行销售,该系统搭载8个A100GPU,一个由5台DGXA100系统组成的机架可替代一个包括AI训练和推理基础设施的数据中心,且功耗仅为其1/20,成本为其1/10,系统售价19.9万美元。因此,在中性假设条件下,考虑到服务器约占数据中心成本的70%(中商产业研究院),则ChatGPT运营一年将需要6741个DGXA100系统用于支撑访问量。因此我们推断,在高昂成本及大数据量需求的限制下,仅有限数量的科技巨头具备参与AI竞赛的实力。

ChatGPT带动大模型竞品发布,海内外科技巨头先后加码AI布局。1)谷歌向AI公司Anthropic投资近4亿美元,后者正在测试生成式AI工具Claude,且谷歌也推出对标ChatGPT的聊天机器人Bard。2)微软以100亿美元投资ChatGPT的开发商OpenAI,并获得其49%股权。2023年2月,微软发布基于ChatGPT的newBing。3)亚马逊云服务AWS宣布与AI公司HuggingFace开展合作,HuggingFace将在AWS上开发针对ChatGPT的开源竞品,构建开源语言模型的下个版本Bloom。4)阿里达摩院正研发类ChatGPT的对话机器人,目前已处于内测阶段。5)百度开发类ChatGPT项目“文心一言”(ERINEBot)。6)京东推出产业版ChatJD。

基于昆仑芯+飞桨+文心大模型AI底座,百度推出“文心一言”拉开国产生成式AI序幕。2023年3月16日,百度正式推出国内首款生成式AI产品“文心一言”,可支持文学创作、文案创作、数理推算、多模态生成等功能,目前已有多家厂商宣布接入。“文心一言”基于全栈自研的AI基础设施进行学习和训练:昆仑芯2代AI芯片:“文心一言”的芯片层核心能力,采用自研XPU-R架构,通用性和性能显著提升;256TOPS@INT8和128TFLOPS@FP16的算力水平,较一代提升2-3倍,保障“文心一言”算力需求;采用7nm先进工艺,GDDR6高速显存,支持虚拟化,芯片间互联和视频编解码等功能。飞桨深度学习平台:“文心一言”的框架层核心能力,系业内首个动静统一的框架、首个通用异构参数服务器架构,支持端边云多硬件和多操作系统,为文心大模型提供有效、快捷、完整的训练框架。

文心知识增强大模型:“文心一言”的模型层核心能力,该产品主要采用ERNIE系列文心NLP模型,拥有千亿参数级别的ERNIE3.0Zeus为该系列最新模型,进一步提升了模型对于不同下游任务的建模能力,大大拓宽了“文心一言”的应用场景。我们认为,随着国产AI大模型应用的不断拓展,算力基础设施加速升级,伴随产业链自主研发需求及地缘政治不确定性,关于进口高端AI芯片及服务器中美博弈升级,国产高算力GPU芯片、服务器及数据中心等厂商有望加速迭代,长期充分受益。

1.5.以GPT-3为例测算:大算力需求驱动AI硬件市场空间提升

GPT-3(GenerativePre-trainedTransformer是GPT-3.5的上一代语言模型,目前一般所说的GPT-3即为拥有1750亿参数的最大GPT-3模型,OpenAI在公开发表的论文《LanguageModelsareFew-ShotLearners》中对GPT-3模型进行了详细分析。对于以ChatGPT为例的大模型算力需求,根据测算,我们预计用于高端GPGPU显卡的训练及推理部分市场空间合计约145.32亿元,其中训练市场规模为27.84亿元,推理市场规模为117.48亿元。

1.6.GPT-4模型算力需求扩增,架构升级降本增效未来可期

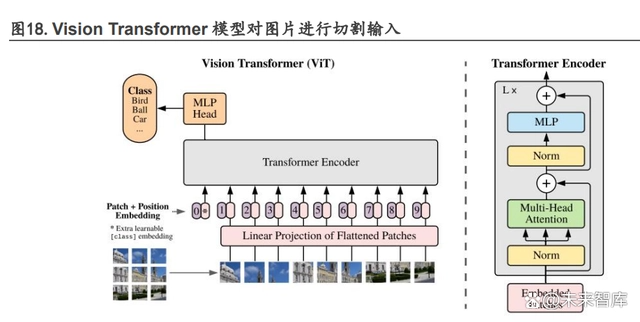

根据OpenAI官网显示,目前GPT-4每4小时只能处理100条消息,且并没有开放图片识别功能。大模型升级带来的运算需求逐渐加码,且可推测目前算力已处于供不应求状态。多模态拓展,图片识别算力需求升级十倍以上。关于从图片到token的转换方式,OpenAI未公布GPT-4的模型参数,假设GPT-4处理图片视觉任务使用VisionTransformer模型(ViT),则输入图片尺寸必须为224×224(ViT-B/16版本)。根据2021年ICLR论文,模型原理大致为把一张图片分成nxn个Patch,每一个Patch作为一个Token。即把一张224×224×3的图片,切分为16×16大小的Patch,每个Patch是三通道小图片,得到16×16×3=768个token并作为向量输入。相较之下,根据前文GPT-3部分假设,假设每个文字问题50-100词,即67-133token。我们可以粗略推论,图像识别的所需算力是文字推理部分所需算力的十倍以上级别。

编译器性能升级,带动大模型产品加速迭代。随着2023年3月15日Pytorch2.0正式版的发布,编译器的性能有大幅提升。Pytorch作为主流深度学习框架,用于构建及训练深度学习模型。Pytorch2.0正式版包含的新高性能TransformAPI能使GPT-3等使用的先进transformer模型的训练和部署更加容易、快速。根据PyTorch基金会数据,在NvidiaA100GPU上使用PyTorch2.0对163个开源模型进行的基准测试,其中包括图像分类、目标检测、图像生成,以及各种NLP任务,2.0版本的编译时间比1.0提高43%。我们认为,编译器性能的提升带动AI大模型编译时间缩短,新产品推出进展或将超预期。

同时我们认为,目前模型的计算成本高,参数量大,长期看模型架构的升级将缩小训练成本,并拓宽边缘设备等部署场景,对算力的需求有望从单模型所需芯片价值量高的推演转变为应用场景快速拓展的量的增长。

(1)根据Nature2023年3月8日文章,有观点认为,更大参数量的模型只是在回答训练数据相关范围的查询上表现更好,并不具备获得回答新问题的更优能力。过往几年,AI大模型的训练使用更高的算力和参数量,但一些小型性能好的模型涌现,在训练中用了更高数据。具体而言,2023年2月Meta发布LLaMA小参数模型,130亿参数但训练量多达1.4万亿个,表现优于GPT-3。而同年3月14日,斯坦福发布基于LLaMA的AIpaca7B微调模型,其52000个指令的OpenAIAPI总成本不到500美元;微调过程在云计算平台使用8个A10080GBGPU,用时3小时,成本约100美元。测试结果表明AIpaca7B性能和其指令资料来源的GPT-3模型相近。长期来看,大模型有望向规模更小、更智能高效的方向演进。

(2)多模态方面,举例说明,根据清华大学2021年论文<DynamicViT:EffificientVisionTransformerswithDynamicTokenSparsifification>,ViT的最终预测仅基于信息最丰富的token的一个子集,该子集足以进行图像准确识别,论文提出的动态token稀疏化框架可以理解为轻量化预测模块,估计每个token的重要性,从而动态删除冗余token,其框架的结论减少了31-37%FLOPS,提升40%以上吞吐量,同时精度下降小于5%。

1.7.英伟达引领硬件端产品升级,国产GPU静待花开

大GPU优势在于通过并行计算实现大量重复性计算。GPGPU(GeneralPurposeGPU)即通用GPU,能够帮助CPU进行非图形相关程序的运算。在类似的价格和功率范围内,GPU能提供比CPU高得多的指令吞吐量和内存带宽。GPGPU架构设计时去掉了GPU为了图形处理而设计的加速硬件单元,保留了GPU的SIMT(SingleInstructionMultipleThreads)架构和通用计算单元,通过GPU多条流水线的并行计算来实现大量计算。所以基于GPU的图形任务无法直接运行在GPGPU上,但对于科学计算,AI训练、推理任务(主要是矩阵运算)等通用计算类型的任务仍然保留了GPU的优势,即高效的搬运和运算有海量数据的重复性任务。目前主要用于例如物理计算、加密解密、科学计算以及比特币等加密货币的生成。

英伟达CUDA架构引领GPGPU开发市场,算力底座筑造核心护城河。随着超算等高并发性计算的需求不断提升,英伟达以推动GPU从专用计算芯片走向通用计算处理器为目标推出了GPGPU,并于2006年前瞻性发布并行编程模型CUDA,以及对应工业标准的OpenCL。CUDA是英伟达的一种通用并行计算平台和编程模型,它通过利用图形处理器(GPU)的处理能力,可大幅提升计算性能。CUDA使英伟达的GPU能够执行使用C、C++、Fortran、OpenCL、DirectCompute和其他语言编写的程序。在CUDA问世之前,对GPU编程必须要编写大量的底层语言代码;CUDA可以让普通程序员可以利用C语言、C++等为CUDA架构编写程序在GPU平台上进行大规模并行计算,在全球GPGPU开发市场占比已超过80%。GPGPU与CUDA组成的软硬件底座,构成了英伟达引领AI计算及数据中心领域的根基。

通过与云计算平台的集成,CUDA可在未购买GPU硬件的基础上提供强大计算能力。例如,假设客户需要训练一个深度学习模型需要大量的计算资源和时间,通过在AWS上租用一个带有NVIDIAGPU的实例,并在该实例上安装CUDA,客户可以使用CUDAAPI和库来利用GPU的计算能力运行计算密集型工作负载,从而可以无需购买GPU硬件并快速完成训练任务。除了AWS,其他云计算提供商如MicrosoftAzure、GoogleCloudPlatform等也提供了与CUDA集成的服务。这些服务可以为客户提供强大的GPU计算能力,从而加速计算密集型工作负载的处理速度。

GPU架构升级过程计算能力不断强化,Hopper架构适用于高性能计算(HPC)和AI工作负载。英伟达在架构设计上,不断加强GPU的计算能力和能源效率。在英伟达GPU架构的演变中,从最先Tesla架构,分别经过Fermi、Kepler、Maxwell、Pascal、Volta、Turing、Ampere至发展为今天的Hopper架构。以Pascal架构为分界点,自2016年后英伟达逐步开始向深度学习方向演进。根据英伟达官网,Pascal架构,与上一代Maxwell相比,神经网络训练速度提高12倍多,并将深度学习推理吞吐量提升了7倍。Volta架构,配备640个Tensor内核增强性能,可提供每秒超过100万亿次(TFLOPS)的深度学习性能,是上一代Pascal架构的5倍以上。Turing架构,配备全新TensorCore,每秒可提供高达500万亿次的张量运算。Ampere架构,采用全新精度标准TensorFloat32(TF32),无需更改任何程序代码即可将AI训练速度提升至20倍。最新Hopper架构是第一个真正异构加速平台,采用台积电4nm工艺,拥有超800亿晶体管,主要由HopperGPU、GraceCPU、NVLINKC2C互联和NVSwitch交换芯片组成,根据英伟达官网介绍,其性能相较于上一代Megatron530B拥有30倍AI推理速度的提升。

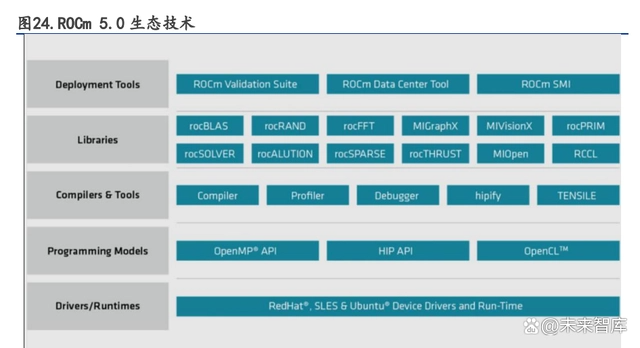

AMD数据中心领域布局全面,形成CPU+GPU+FPGA+DPU产品矩阵。与英伟达相比,AMD在服务器端CPU业务表现较好,根据Passmark数据显示,2021年Q4AMDEPYC霄龙系列在英特尔垄断下有所增长,占全球服务器CPU市场的6%。依据CPU业务的优势,AMD在研发GPGPU产品时推出InfinityFapic技术,将EPYC霄龙系列CPU与InstinctMI系列GPU直接相连,实现一致的高速缓存,形成协同效应。此外,AMD分别于2022年2月、4月收购Xilinx和Pensando,补齐FPGA与DPU短板,全面进军数据中心领域。软件方面,AMD推出ROCm平台打造CDNA架构,但无法替代英伟达CUDA生态。AMD最新的面向GPGPU架构为CDNA系列架构,CDNA架构使用ROCm自主生态进行编写。AMD的ROCm生态采取HIP编程模型,但HIP与CUDA的编程语法极为相似,开发者可以模仿CUDA的编程方式为AMD的GPU产品编程,从而在源代码层面上兼容CUDA。所以从本质上来看,ROCm生态只是借用了CUDA的技术,无法真正替代CUDA产生壁垒。

前瞻性布局AI和云计算领域,英伟达独占鳌头。回顾英伟达发展历程,在传统游戏业务外,公司始终关注数据中心业务布局:英伟达早在2006年便推出CUDA架构,提高GPU解决复杂计算的能力;2007年推出专为高性能计算设计的Tesla系列GPU产品,此后开始快速迭代,性能不断提升,至今已发展出8个架构;2016年推出世上首款台式超级计算机DGX-1,主要应用于AI领域;2019年收购Mellanox,降低云数据中心的运营成本。与AMD、英特尔相比,英伟达在AI计算领域独占鳌头:在2020年全球TOP500超级计算机榜单中,有333台超级计算机采用了英伟达的技术,占总数的66.6%,英伟达的统治地位可见一斑。

软硬件共同布局形成生态系统,造就英伟达核心技术壁垒。

硬件端:基于GPU、DPU和CPU构建英伟达加速计算平台生态:(1)主要产品TeslaGPU系列迭代速度快,从2008年至2022年,先后推出8种GPU架构,平均两年多推出新架构,半年推出新产品。超快的迭代速度使英伟达的GPU性能走在AI芯片行业前沿,引领人工智能计算领域发生变革。(2)DPU方面,英伟达于2019年战略性收购以色列超算以太网公司Mellanox,利用其InfiniBand(无限带宽)技术设计出Bluefield系列DPU芯片,弥补其生态在数据交互方面的不足。InfiniBand与以太网相同,是一种计算机网络通信标准,但它具有极高的吞吐量和极低的延迟,通常用于超级计算机的互联。英伟达的BluefieldDPU芯片可用于分担CPU的网络连接算力需求,从而提高云数据中心的效率,降低运营成本。(3)CPU方面,自主设计GraceCPU并推出GraceHopper超级芯片,解决内存带宽瓶颈问题。采用x86CPU的传统数据中心会受到PCIe总线规格的限制,CPU到GPU的带宽较小,计算效率受到影响;而GraceHopper超级芯片提供自研GraceCPU+GPU相结合的一致内存模型,从而可以使用英伟达NVLink-C2C技术快速传输,其带宽是第5代PCIe带宽的7倍,极大提高了数据中心的运行性能。

相较于A100GPU,H100性能再次大幅提升。在H100配备第四代TensorCore和Transformer引擎(FP8精度),同上一代A100相比,AI推理能力提升30倍。其核心采用的是TSMC目前最先进的4nm工艺,H100使用双精度TensorCore的FLOPS提升3倍。

国内GPGPU生态起步较晚,国产GPU亟待补位。根据华为2021年9月发布的《智能世界2030》报告,人类将于2030年进入YB数据时代,通用算力相较2020年增长10倍、人工智能算力国产GPU厂商的核心架构多为自研,难度极高,需投入海量资金以及高昂的人力和时间成本。由于我国GPU行业起步较晚,缺乏相应生态,目前同国际一流厂商仍存在较大差距。在中美摩擦加剧、经济全球化逆行的背景下,以海光信息、天数智芯、壁仞科技和摩尔线程等为代表的国内GPU厂商进展迅速,国产GPU自主可控未来可期。

2.大算力场景遇到的问题及解决途径

2.1.“内存墙”、“功耗墙”等掣肘AI的算力发展

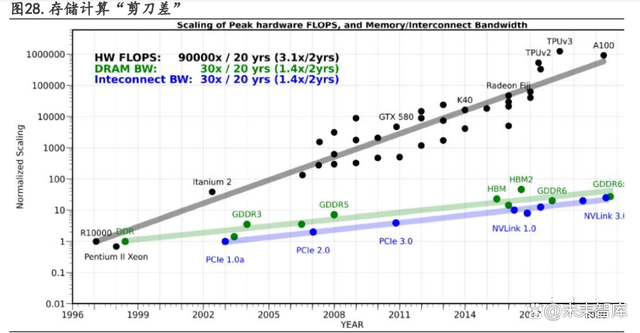

“存”“算”性能失配,内存墙导致访存时延高,效率低。内存墙,指内存的容量或传输带宽有限而严重限制CPU性能发挥的现象。内存的性能指标主要有“带宽”(Bandwidth)和“等待时间”(Latency)。近20年间,运算设备的算力提高了90000倍,提升非常快。虽然存储器从DDR发展到GDDR6x,能够用于显卡、游戏终端和高性能运算,接口标准也从PCIe1.0a升级到NVLink3.0,但是通讯带宽的增长只有30倍,和算力相比提高幅度非常缓慢。

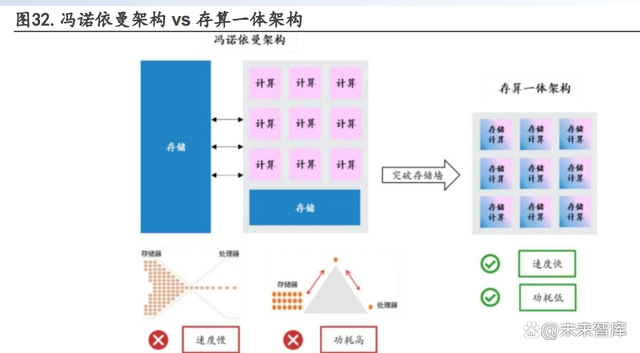

冯诺依曼架构下,数据传输导致严重的功耗损失。冯·诺依曼架构要求数据在存储器单元和处理单元之间不断地“读写”,这样数据在两者之间来回传输就会消耗很多的传输功耗。根据英特尔的研究表明,当半导体工艺达到7nm时,数据搬运功耗高达35pJ/bit,占总功耗的63.7%。数据传输造成的功耗损失越来越严重,限制了芯片发展的速度和效率,形成了“功耗墙”问题。

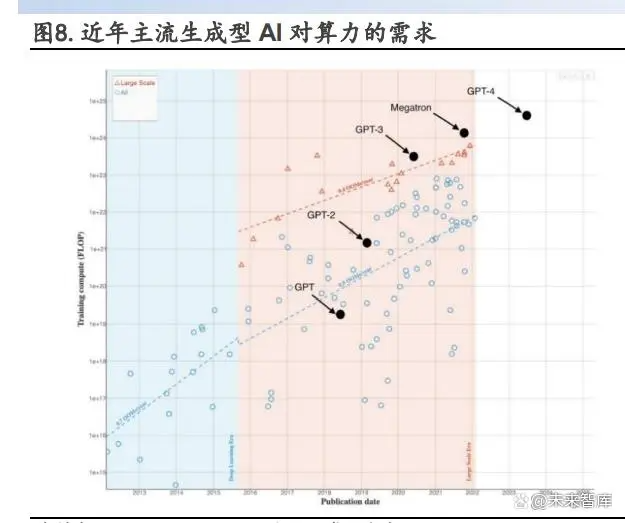

AI模型参数量极速扩大,GPU内存增长速度捉襟见肘。在GPT-2之前的模型时代,GPU内存还能满足AI大模型的需求。近年来,随着Transformer模型的大规模发展和应用,模型大小每两年平均增长了240倍。GPT-3等大模型的参数增长已经超过了GPU内存的增长。传统的设计趋势已经不能适应当前的需求,芯片内部、芯片之间或AI加速器之间的通信成为了AI训练的瓶颈。AI训练不可避免地遇到了“内存墙”问题。

AI模型运算量增长速度不断加快,推动硬件算力增长。预训练技术的进步导致了各领域模型计算量的快速增长,大约每两年就要增加15倍。而Transformer类模型的运算量更是每两年就要增加750倍。这种近乎指数的增长趋势促使AI硬件的研发方向发生变化,需要更高的峰值算力。当前的研究为了实现更高的算力,甚至不惜简化或者优化其他部分组件,例如内存的分层架构,将DRAM容量用于需要高性能访问的热数据,将容量层用于处理需要大容量但性能要求不那么高的任务,以适应不同的数据类型、用例、技术需求和预算限制,适用于AI、ML和HPC等众多应用场景,能帮助企业以经济高效的方式满足内存需求。

2.2.“内存墙”、“功耗墙”等问题解决路径

2.2.1.存算一体技术:以SRAM、RRAM为主的新架构,大算力领域优势大

存算一体在存储器中嵌入计算能力,以新的运算架构进行乘加运算。存算一体是一种以数据为中心的非冯诺依曼架构,它将存储功能和计算功能有机结合起来,直接在存储单元中处理数据。存算一体通过改造“读”电路的存内计算架构,可以直接从“读”电路中得到运算结果,并将结果“写”回存储器的目标地址,避免了在存储单元和计算单元之间频繁地转移数据。存算一体减少了不必要的数据搬移造成的开销,不仅大幅降低了功耗(降至1/10~1/100),还可以利用存储单元进行逻辑计算提高算力,显著提升计算效率。它不仅适用于AI计算,也适用于感存算一体芯片和类脑芯片,是未来大数据计算芯片架构的主流方向。

SRAM、RRAM是存算一体介质的主流研究方向。存算一体的成熟存储器有几种,比如NORFLASH、SRAM、DRAM、RRAM、MRAM等NVRAM。FLASH是非易失性存储,成本低,可靠性高,但制程有瓶颈。SRAM速度快,能效比高,在存内逻辑技术发展后有高能效和高精度的特点。DRAM容量大,成本低,但速度慢,需要不断刷新电力。新型存储器PCAM、MRAM、RRAM和FRAM也适用于存算一体。其中RRAM在神经网络计算中有优势,是下一代存算一体介质的主流方向之一。除了SRAM之外,RRAM也是未来发展最快的新型存储器之一,它结构简单,速度高,但材料不稳定,工艺还需2-5年才能成熟。

存算一体有着广泛的应用场景,在不同大小设备上均有需求。

从技术领域来看,存算一体可以应用于:(1)AI和大数据计算:将AI计算中大量乘加计算的权重部分存在存储单元中,从而在读取的同时进行数据输入和计算处理,在存储阵列中完成卷积运算。(2)感存算一体:集传感、储存和运算为一体构建感存算一体架构,在传感器自身包含的AI存算一体芯片上运算,来实现零延时和超低功耗的智能视觉处理能力。(3)类脑计算:使计算机像人脑一样将存储和计算合二为一,从而高速处理信息。存算一体天然是将存储和计算结合在一起的技术,是未来类脑计算的首选和产品快速落地的关键。

从应用场景来分,存算一体可以适用于各类人工智能场景和元宇宙计算,如可穿戴设备、移动终端、智能驾驶、数据中心等。(1)针对端侧的可穿戴等小设备,对成本、功耗、时延难度很敏感。端侧竞品众多,应用场景碎片化,面临成本与功效的难题。存算一体技术在端侧的竞争力影响约占30%。(例如arm占30%,降噪或ISP占40%,AI加速能力只占30%)(2)针对云计算和边缘计算的大算力设备,是存算一体芯片的优势领域。存算一体在大算力领域的竞争力影响约占90%。

传统存储大厂纷纷入局,新兴公司不断涌现。(1)国外方面,三星电子在多个技术路线进行尝试,发布新型HBM-PIM(存内计算)芯片、全球首个基于MRAM(磁性随机存储器)的存内计算研究等。台积电在ISSCC2021上提出基于数字改良的SRAM设计存内计算方案。英特尔也早早提出近内存计算战略,将数据在存储层级向上移动,使其更接近处理单元进行计算。(2)国内方面,阿里达摩院成功研发全球首款基于DRAM的3D键合堆叠存算一体芯片,可突破冯·诺依曼架构的性能瓶颈。千芯科技是可重构存算一体AI芯片的领导者和先驱,核心产品包括高算力低功耗的存算一体AI芯片/IP核(支持多领域多模态人工智能算法)。后摩智能致力于突破智能计算芯片性能及功耗瓶颈,其提供的大算力、低功耗的高能效比芯片及解决方案,可应用于无人车、泛机器人等边缘端,以及云端推荐、图像分析等云端推理场景。

2.2.2.HBM技术:高吞吐高带宽,AI带动需求激增

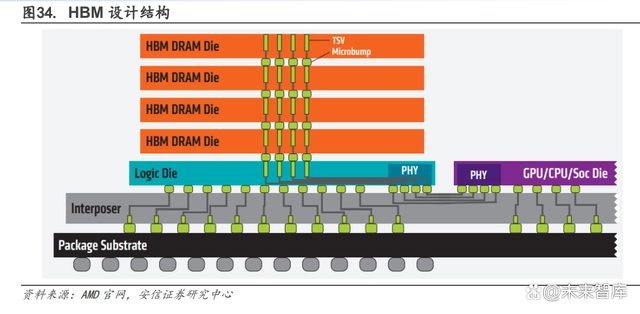

HBM(HighBandwidthMemory)意为高带宽存储器,是一种硬件存储介质,是高性能GPU的核心组件。HBM具有高吞吐高带宽的特性,受到工业界和学术界的关注。它单颗粒的带宽可以达到256GB/s,远超过DDR4和GDDR6。DDR4是CPU和硬件处理单元的常用外挂存储设备,但是它的吞吐能力不足以满足当今计算需求,特别是在AI计算、区块链和数字货币挖矿等大数据处理访存需求极高的领域。GDDR6也比不上HBM,它单颗粒的带宽只有64GB/s,是HBM的1/4。而DDR43200需要至少8颗粒才能提供25.6GB/s的带宽,是HBM的1/10。HBM使用多根数据线实现高带宽,完美解决传统存储效率低的问题。HBM的核心原理和普通的DDR、GDDR完全一样,但是HBM使用多根数据线实现了高带宽。HBM/HBM2使用1024根数据线传输数据,作为对比,GDDR是32根,DDR是64根。HBM需要使用额外的硅联通层,通过晶片堆叠技术与处理器连接。这么多的连接线保持高传输频率会带来高功耗。因此HBM的数据传输频率相对很低,HBM2也只有2Gbps,作为对比,GDDR6是16Gbps,DDR43200是3.2Gbps。这些特点导致了HBM技术高成本,容量不可扩,高延迟等缺点。

HBM可以被广泛的应用到汽车高带宽存储器,GPU显存芯片,部分CPU的内存芯片,边缘AI加速卡,Chiplets等硬件中。在高端GPU芯片产品中,比如NVDIA面向数据中心的A100等加速卡中就使用了HBM;部分CPU的内存芯片,如目前富岳中的A64FX等HPC芯片中也有应用到。车辆在快速移动时,摄像头、传感器会捕获大量的数据,为了更快速的处理数据,HBM是最合适的选择。Chiplets在设计过程中没有降低对内存的需求,随着异构计算(尤其是小芯片)的发展,芯片会加速对高带宽内存的需求,无论是HBM、GDDR6还是LPDDR6。

HBM缓解带宽瓶颈,是AI时代不可或缺的关键技术。AI处理器架构的探讨从学术界开始,当时的模型简单,算力低,后来模型加深,算力需求增加,带宽瓶颈出现,也就是IO问题。这个问题可以通过增大片内缓存、优化调度模型等方法解决。但是随着AI大模型和云端AI处理的发展,计算单元剧增,IO问题更严重了。要解决这个问题需要付出很高的代价(比如增加DDR接口通道数量、片内缓存容量、多芯片互联),这便是HBM出现的意义。HBM用晶片堆叠技术和硅联通层把处理器和存储器连接起来,把AI/深度学习完全放到片上,提高集成度,降低功耗,不受芯片引脚数量的限制。HBM在一定程度上解决了IO瓶颈。未来人工智能的数据量、计算量会越来越大,超过现有的DDR/GDDR带宽瓶颈,HBM可能会是唯一的解决方案。

巨头领跑,各大存储公司都已在HBM领域参与角逐。SK海力士、三星、美光等存储巨头在HBM领域展开了升级竞赛,国内佰维存储等公司持续关注HBM领域。SK海力士早在2021年10月就开发出全球首款HBM3,2022年6月量产了HBM3DRAM芯片,并将供货英伟达,持续巩固其市场领先地位。三星也在积极跟进,在2022年技术发布会上发布的内存技术发展路线图中,HBM3技术已经量产。伴随着ChatGPT的火热,整个市场对于高性能计算卡等硬件产品的需求水涨船高,上游大厂如三星和海力士目前的DRAM业务相关订单激增。GPU公司英伟达一直在要求SK海力士提供最新的HBM3内存颗粒。服务器CPU公司英特尔在全新的第四代至强可扩展处理器当中也推出了配备SK海力士HBM的产品。

2.2.3.Chiplet技术:全产业链升级降本增效,国内外大厂前瞻布局

Chiplet即根据计算单元或功能单元将SOC进行分解,分别选择合适制程工艺制造。随着处理器的核越来越多,芯片复杂度增加、设计周期越来越长,SoC芯片验证的时间、成本也急剧增加,特别是高端处理芯片、大芯片。当前集成电路工艺在物理、化学很多方面都达到了极限,大芯片快要接近制造瓶颈,传统的SoC已经很难继续被采纳。Chiplet,俗称小芯片、芯粒,是将一块原本复杂的SoC芯片,从设计的时候就按照不同的计算单元或功能单元进行分解,然后每个单元分别选择最合适的半导体制程工艺进行制造,再通过先进封装技术将各自单元彼此互联。Chiplet是一种类似搭乐高积木的方法,能将采用不同制造商、不同制程工艺的各种功能芯片进行组装,从而实现更高良率、更低成本。

Chiplet可以从多个维度降低成本,延续摩尔定律的“经济效益”。随着半导体工艺制程推进,晶体管尺寸越来越逼近物理极限,所耗费的时间及成本越来越高,同时所能够带来的“经济效益”的也越来越有限。Chiplet技术可从三个不同的维度来降低成本:(1)可大幅度提高大型芯片的良率:芯片的良率与芯片面积有关,Chiplet设计将大芯片分成小模块可以有效改善良率,降低因不良率导致的成本增加。(2)可降低设计的复杂度和设计成本:Chiplet通过在芯片设计阶段就将Soc按照不同功能模块分解成可重复云涌的小芯粒,是一种新形式的IP复用,可大幅度降低设计复杂度和成本累次增加。(3)可降低芯片制造的成本:在Soc中的一些主要逻辑计算单元是依赖于先进工艺制程来提升性能,但其他部分对制程的要求并不高,一些成熟制程即可满足需求。将Soc进行Chiplet化后对于不同的芯粒可选择对应合适的工艺制程进行分开制造,极大降低芯片的制造成本。

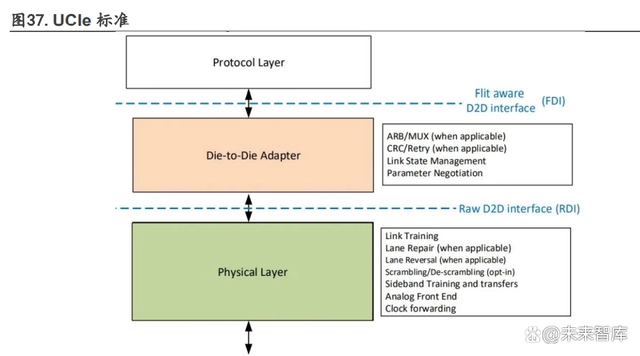

Chiplet为全产业链提供了升级机会。在后摩尔时代,Chiplet可以开启一个新的芯片生态。2022年3月,Chiplet的高速互联标准——UCIe(UniversalChipletInterconnectExpress,通用芯粒互联技术)正式推出,旨在芯片封装层面确立互联互通的统一标准,打造一个开放性的Chiplet生态系统。巨头们合力搭建起了统一的Chiplet互联标准,将加速推动开放的Chiplet平台发展,并横跨x86、Arm、RISC-V等架构和指令集。Chiplet的影响力也从设计端走到芯片制造与封装环节。在芯片小型化的设计过程中,需要添加更多I/O与其他芯片芯片接口,裸片尺寸必须要保持较大的空白空间。而且,要想保证Chiplet的信号传输质量就需要发展高密度、大宽带布线的先进封装技术。另外,Chiplet也影响到从EDA厂商、晶圆制造和封装公司、芯粒IP供应商、Chiplet产品及系统设计公司到Fabless设计厂商的产业链各个环节的参与者。

乾坤未定,Chiplet是国内芯片相关公司的重要发展机遇。(1)最先受到影响的是芯片IP设计企业,Chiplet本质就是不同的IP芯片化,国内类似IP商均有望参与其中,比如华为海思有IP甚至指令集开发实力的公司,推出基于RISC-V内核的处理器(玄铁910)阿里平头哥半导体公司,独立的第三方IP厂商,如芯动科技、芯原股份、芯耀辉、锐成芯微、芯来等众多IP公司等。(2)Chiplet需要EDA工具从架构探索、芯片设计、物理及封装实现等提供全面支持,为国内EDA企业发展带来了突破口。芯和半导体已全面支持2.5DInterposer、3DIC和Chiplet设计。(3)Chiplet也推动了先进封装技术的发展。根据长电科技公告,在封测技术领域取得新的突破。4nm芯片作为先进硅节点技术,是导入Chiplet封装的一部分通富微电提供晶圆级及基板级封装两种解决方案,其中晶圆级TSV技术是Chiplet技术路径的一个重要部分。

国外芯片厂率先发力,通过Chiplet实现收益。AMD的EPYC率先采用了Chiplet结构,实现了在服务器CPU市场上的翻身。随后,Ryzen产品上重用了EYPCRome的CCD,这样的chiplet设计极好的降低了总研发费用。2023年1月,Intel发布了采用了Chiplet技术的第四代至强可扩展处理器SapphireRapids以及英特尔数据中心GPUMax系列等。SapphireRapids是Intel首个基于Chiplet设计的处理器,被称为“算力神器”。Xilinx的2011Virtex-72000T是4个裸片的Chiplet设计。Xilinx也是业界唯一的同构和异构的3DIC。

2.2.4.CPO技术:提升数据中心及云计算效率,应用领域广泛

CPO(Co-packaged,共封装光学技术)是高速电信号能够高质量的在交换芯片和光引擎之间传输。在5G时代,计算、传输、存储的带宽要求越来越高,同时硅光技术也越来越成熟,因此板上和板间的光互连成为了一种必要的方式。随着通道数大幅增加,需要专用集成电路(ASIC)来控制多个光收发模块。传统的连接方式是Pluggable(可插拔),即光引擎是可插拔的光模块,通过光纤和SerDes通道与网络交换芯片(AISC)连接。之后发展出了NPO(Nearpackaged,近封装光学),一种将光引擎和交换芯片分别装配在同一块PCB基板上的方式。而CPO是一种将交换芯片和光引擎共同装配在同一个Socketed(插槽)上的方式,形成芯片和模组的共封装,从而降低网络设备的功耗和散热问题。NPO是CPO的过渡阶段,相对容易实现,而CPO是最终解决方案。

随着大数据及AI的发展,数据中心的需求激增,CPO有着广泛的应用前景。在数据中心领域,CPO技术可以实现更高的数据密度和更快的数据传输速度,还可以减少系统的功耗和空间占用,降低数据中心的能源消耗和维护成本,能够应用于高速网络交换、服务器互联和分布式存储等领域,例如,Facebook在其自研的数据中心网络FapicAggregator中采用了CPO技术,提高了网络的速度和质量。在云计算领域,CPO技术可以实现高速云计算和大规模数据处理。例如微软在其云计算平台Azure中采用了CPO技术,实现更高的数据密度和更快的数据传输速度,提高云计算的效率和性能。在5G通信领域,CPO技术可以实现更快的无线数据传输和更稳定的网络连接。例如华为在其5G通信系统中采用了CPO技术,将收发器和芯片封装在同一个封装体中,从而实现了高速、高密度、低功耗的通信。除此之外,5G/6G用户的增加,人工智能、机器学习(ML)、物联网(IoT)和虚拟现实流量的延迟敏感型流量激增,对光收发器的数据速率要求将快速增长;AI、ML、VR和AR对数据中心的带宽要求巨大,并且对低延迟有极高的要求,未来CPO的市场规模将持续高速扩大。

CPO技术壁垒高,通信公司成为主要参与者,发展迅速。锐捷网络于2022年正式推出了首款应用CPO技术的数据中心交换机,截至目前正式发布了多款同时应用硅光技术和液冷技术的交换机,散热成本对比同性能的可插拔光模块设备降低了35%。联特科技专注研发基于EML(电吸收调制激器)、SIP(硅光)、TFLN(薄膜铌酸锂)调制技术的800G光模块,以及用于下一代产品NPO(近封装光学)/CPO(共封装光学)所需的高速光连接技术、激光器技术和芯片级光电混合封装技术等。新易盛的光膜块400G已广泛应用在各大数据中心,更高端的800G已实现产业化出货走在行业引领前端,且光模块已突破低功耗极限,同时布局了光电共同封装(CPO)技术,双重受益,行业需求增量大。中际旭创400G系列相干产品已逐步在国内主流设备商和互联网云厂商中得到了应用,同时也发布了800G的解决方案,部分光模块使用自家研制的硅光芯片。